Program Name

: Diploma in Information Technology

**Program Code**

: IF

Semester

: Third

**Course Title**

: Digital Techniques and Microprocessor

**Course Code**

: 22323

#### 1. RATIONALE

It is essential to know fundamentals of digital electronics to understand the concept of microprocessor and its application. Microprocessor benefits to meet challenges of growing applications of advanced microprocessor based technologies hence students are expected to be conversant with components of microprocessors and microprocessor based programming. This course is designed to help the students to design logic circuits and to understand the architecture of 8086 microprocessor. The course also enables students to develop assembly language programs using instruction set of 8086 Microprocessor.

#### 2. COMPETENCY

The aim of this course is to help the student to attain the following industry identified competency through various teaching learning experiences:

Build digital systems including microprocessor based systems.

#### 3. COURSE OUTCOMES (COs)

The theory, practical experiences and relevant soft skills associated with this course are to be taught and implemented, so that the student demonstrates the following *industry oriented* COs associated with the above mentioned competency:

- a. Test the Digital Systems, Logic Families and logic gates

- b. Construct combinational logical circuit

- c. Construct sequential logical circuit

- d. Use registers and instructions of 8086.

- e. Develop assembly language programs using 8086.

#### 4. TEACHING AND EXAMINATION SCHEME

| Teaching<br>Scheme |   |   |         |        | Examination Scheme |     |           |     |     |     |     |     |     |     |     |     |

|--------------------|---|---|---------|--------|--------------------|-----|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                    |   |   | Credit  | Theory |                    |     | Practical |     |     |     |     |     |     |     |     |     |

| L                  | Т | P | (L+T+P) | Paper  | ES                 | SE  | P         | ١   | Tot | al  | ES  | E   | P   | 'A  | То  | tal |

|                    |   |   |         | Hrs.   | Max                | Min | Max       | Min | Max | Min | Max | Min | Max | Min | Max | Min |

| 4                  | 1 | 2 | 6       | 3      | 70                 | 28  | 30*       | 00  | 100 | 40  | 25@ | 10  | 25  | 10  | 50  | 20  |

(\*): Under the theory PA; Out of 30 marks, 10 marks of theory PA are for micro-project assessment to facilitate integration of COs and the remaining 20 marks is the average of 2 tests to be taken during the semester for the assessment of the UOs required for the attainment of the COs.

**Legends:** L-Lecture; T – Tutorial/Teacher Guided Theory Practice; P - Practical; C – Credit, ESE - End Semester Examination; PA - Progressive Assessment.

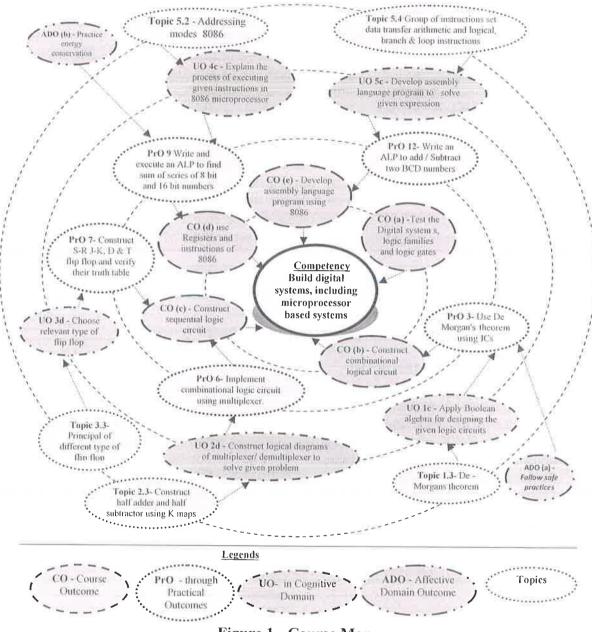

5. COURSE MAP (with sample COs. Pros. LOs. ADOs and topics)

This course map illustrates an overview of the flow and takages of the topics at various levels

of outcomes (details in subsequent sections) to be attained by the student by the end of the course, in all domains of learning in terms of the industry/employer identified competency depicted at the centre of this map.

Figure 1 - Course Map

# 6. SUGGESTED PRACTICALS/ EXERCISES

The practicals in this section are PrOs (i.e. sub-components of the COs) to be developed and assessed in the student for the attainment of the competency.

| S.<br>No. | Practical Outcomes (PrOs)                                          | Unit<br>No. | Approx.<br>Hrs.<br>Required |

|-----------|--------------------------------------------------------------------|-------------|-----------------------------|

| 1         | Test truth tables of basic logic gates using Transistor-Transistor | I           | 02                          |

|           | Logic (TTL) Integrated Circuits (ICs) -                            |             |                             |

| 2         | Check truth tables of universal logic and NOR)                     | I           | 02*                         |

|           | using Transistor-Transistor Logic (TL) Integraled Circuits         |             |                             |

| S.<br>No. | Practical Outcomes (PrOs)                                                                                                                               |       | Approx.<br>Hrs.<br>Required |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------|--|

|           | (ICs).                                                                                                                                                  |       |                             |  |

| 3         | Check De Morgan's theorem using ICs                                                                                                                     | I     | 02                          |  |

| 4         | Convert given expression to Sum of Product (SOP) form using basic logic gates.                                                                          | II    | 02*                         |  |

| 5         | Convert given expression to Product of Sum (POS) form using basic logic gates.                                                                          | II    | 02                          |  |

| 6         | Implement Combinational Circuit using Multiplexer                                                                                                       | II    | 02                          |  |

| 7         | Construct S-R, J-K, D and T flip-flop and verify their truth tables.                                                                                    | III   | 02*                         |  |

| 8         | Write and execute an Assembly Language Program(ALP) to add / subtract two 8 bit and 16 bit numbers with the help of programming tools and any simulator | V     | 02*                         |  |

| 9         | Write and execute an ALP to find sum of series of 8 bit and 16 bit numbers.                                                                             | V     | 02                          |  |

| 10        | Develop an ALP to multiply two 8 bit and 16 bit numbers. Unsigned/ signed numbers.                                                                      | V     | 02*                         |  |

| 11        | Develop an ALP to divide two 8 bit and 16 bit numbers. Unsigned/ signed numbers.                                                                        | V     | 02                          |  |

| 12        | Write an ALP to add / Subtract two BCD numbers.                                                                                                         | V     | 02                          |  |

| 13        | Write an ALP to multiply / Divide two BCD numbers.                                                                                                      | V     | 02                          |  |

| 14        | Develop an ALP to find smallest and largest number from array of n numbers.                                                                             | V     | 02*                         |  |

| 15        | Develop an ALP to find largest number from array of n numbers.                                                                                          | V     | 02                          |  |

| 16        | Write an ALP to perform block transfer from one memory location to another.                                                                             | V     | 02*                         |  |

|           |                                                                                                                                                         | Total | 32                          |  |

## Note

i. A suggestive list of **PrOs** is given in the above table. More such PrOs can be added to attain the COs and competency. A judicial mix of minimum 12 or more practical need to be performed, out of which, the practicals marked as '\*' are compulsory, so that the student reaches the 'Precision Level' of Dave's 'Psychomotor Domain Taxonomy' as generally required by the industry.

ii. The 'Process' and 'Product' related skills associated with each PrO is to be assessed according to a suggested sample given below:

| S. No. | Performance Indicators                                  | Weightage in % |

|--------|---------------------------------------------------------|----------------|

| 1      | Design digital circuit.                                 | 20             |

| 2      | Implement and test digital circuits                     | 30             |

| 3      | Final design/program output                             | 20             |

| 4      | Answer to sample questions                              | 20             |

| 5      | Submission of design in time with accuracy and neatness | 10             |

|        | Total                                                   | 100            |

The above PrOs also comprise of the following social skills/attitudes which are Affective Domain Outcomes (ADOs) that are best developed through the laboratory/field based

experiences:

- a. Follow safety practices.

- b. Practice good housekeeping.

- c. Demonstrate working as a leader/a team member.

- d. Follow ethical practices.

The ADOs are not specific to any one PrO, but are embedded in many PrOs. Hence, the acquisition of the ADOs takes place gradually in the student when s/he undertakes a series of practical experiences over a period of time. Moreover, the level of achievement of the ADOs according to Krathwohl's 'Affective Domain Taxonomy' should gradually increase as planned below:

- 'Valuing Level' in 1<sup>st</sup> year

- 'Organising Level' in 2<sup>nd</sup> year and

- 'Characterising Level' in 3<sup>rd</sup> year.

# 7. MAJOR EQUIPMENT/ INSTRUMENTS REQUIRED

The major equipment with broad specification mentioned here will usher in uniformity in conduct of experiments, as well as aid to procure equipment by authorities concerned.

| S.<br>No. | Equipment Name with Broad Specifications                                                                                                                                                                                                                                                                                                                 | PrO S. No.            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1         | Digital Multimeter, pulse generator/function generator, DC regulated power supply, Bread boards, connecting wires, Stripper, Soldering Gun, Soldering Metal, Flux, IC Tester, LEDs, Digital ICs, Data sheets of ICs used in Lab.                                                                                                                         | 1 to 8                |

| 2         | Personal Computer Intel Pentium Onwards Minimum 2GB RAM, 500Gbyte HDD) installed with Windows 7 onwards, Any Editor to write/edit programs, Turbo/Macro Assembler (TASM/MASM) Turbo Linker (TLINK/LINK, Turbo Debugger(TD/Debug), (DOSBOX utility for higher end operating systems) (Minimum 20 computers for batch of 20 students) with shared printer. | 9 to 16               |

| 3         | 8086 freeware/open source based simulator to demonstrate internal functioning of microprocessor (Desirable)                                                                                                                                                                                                                                              | Suggested for 9 to 16 |

## 8. UNDERPINNING THEORY COMPONENTS

The following topics are to be taught and assessed in order to develop the sample UOs given below for achieving the COs to attain the identified competency. More UOs could be added:

| Unit                                                                                 | Unit Outcomes (UOs)                                                                                                                                                                                                                                                                                                                                                                                                                                               | Topics and Sub-topics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unit – I<br>Number<br>systems,<br>Digital<br>Logic<br>families<br>and Logic<br>Gates | (in cognitive domain)  1a. Convert the number from the given number system to the specified number system.  1b. Perform the given binary arithmetic operation on the given data.  1c. Describe the characteristics of the given Digital Logic family.  1d. Derive the truth table of the given basic logic gate/ derived logic gate.  1e. Apply Boolean algebra for designing the given logic circuit.  1f. Design the logical circuit for the given application. | 1.1 Terms - Bit, Byte, Nibble 1.2 Number systems – Decimal, Binary, Octal and Hexadecimal and their conversions from one number system to another (Integer and fractional). 1.3 Codes – BCD, Gray, ASCII, EBCDIC 1.4 Binary arithmetic – Compliments – 1's and 2's, Addition, subtraction, multiplication and division.(up to 8 bit) 1.1 Applications of digital circuits, Comparison of TTL,CMOS,ECL, Characteristics of digital ICs.(Propagation Delay, Noise Margin, Power dissipation, Fan-in Fan-out. Threshold logic levels). 1.2 Basic gates(AND,OR,NOT), Derived gates (NAND,NOR,EX- OR,EX-NOR),Universal gates 1.3 Basic logic operations using laws of Boolean algebra. DE Morgan's Theorems. |

| Unit- II<br>Combinati<br>onal Logic<br>Circuits                                      | <ul> <li>2a. Simplify the given logical expression using Sum-of-Product (SOP) and Product-of-Sum (POS) approaches.</li> <li>2b. Minimize the given logical function using Karnaugh's map (K-MAP).</li> <li>2c. Explain the approach of designing the given data for half-adder/half-subtractor using K-MAP.</li> <li>2d. Construct the logical diagrams of multiplexer/demultiplexer to solve the given problem.</li> </ul>                                       | <ul> <li>2.1 Standard/canonical forms for Boolean functions, Min terms and Max terms.</li> <li>2.2 Simplification of logical circuit by way of Sum-of-Product (SOP) and Product-of-Sum (POS) approaches.</li> <li>2.3 Expressions simplification using Boolean algebra techniques (i.e. K-MAP of 2,3,4 variable K-MAPs)</li> <li>2.4 Construction of Half Adder and Half subtractor using K-MAP.</li> <li>2.5 Necessity, principle and types of multiplexer and demultiplexer.</li> </ul>                                                                                                                                                                                                               |

| Unit- III<br>Sequential<br>Logic<br>Circuits                                         | <ul> <li>3a. Differentiate characteristics of the given logic Circuits.</li> <li>3b. Identify the given situations where edge triggering is preferred over level triggering with justification.</li> <li>3c. Explain with sketches the working principle of given pe</li> </ul>                                                                                                                                                                                   | <ul> <li>3.1 Combinational and sequential logic Circuits. Block diagram of sequential circuit</li> <li>3.2 Flip-flops: One-Bit memory Cell symbol applications of flip-flops, Types of triggering flip-flops, Edge triggered and level triggered.</li> <li>3.3 Principle of working of different</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                             |

| Unit                                                                | Unit Outcomes (UOs) (in cognitive domain)                                                                                                                                                                                                                                                                                                                                                                                                                                      | Topics and Sub-topics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     | of flip flop.  3d. Choose relevant type of flip-flop (SR/ JK/ D/T) based on given number of inputs and the manner in which they affect the binary state of the flip-flop.                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Unit-IV Microproc essor: 8086 and Modern Microproc essors           | <ul> <li>4a. Explain the process of executing the given instructions in 8086 microprocessor.</li> <li>4b. Derive physical address to locate the given data from memory Segmentation.</li> <li>4c. Compare architecture of Microprocessor 8086 with the specified processor on the given parameters.</li> <li>4d. Select the CISC/RISC architecture based processor for the given situation with justification.</li> </ul>                                                      | <ul> <li>4.1 Evolution of Microprocessor and type, 16-bit Microprocessor-8086.</li> <li>4.2 Features of 8086, pin diagram and architecture of 8086, Flag register and segment registers of 8086, Minimum mode and maximum mode of operation. Timing diagram. Concept of Memory segmentation and pipelining, physical address generation.</li> <li>4.3 Overview of Pentium Family and processors.</li> <li>4.4 Characteristics of RISC processor.</li> <li>4.5 CISC with RISC in terms of Instruction set, Length, addressing modes.</li> </ul> |

| Unit-V<br>Assembly<br>Language<br>Program<br>ming<br>using<br>8086. | <ul> <li>5a. Select relevant addressing mode of 8086 to identify instruction for solving the given problem with justification</li> <li>5b. Choose relevant instruction to perform the given operation from the instruction set of 8086 with justification.</li> <li>5c. Develop assembly language program to solve the given expression.</li> <li>5d. Develop the assembly language program to solve the given problem using decision making and looping structure.</li> </ul> | <ul> <li>5.1 Programming Model of 8086     assembly language program.</li> <li>5.2 Addressing Modes of 8086 with     examples.</li> <li>5.3 Group of instruction set-Data     transfer, Arithmetic and Logical,     Branch and loop, Flag     manipulation, shift and rotate and     string instructions, (Only format     and examples)</li> <li>5.4 Assembly Language programs for     (8-bit and 16 bit) Addition     subtraction, Multiplication     Division, Decision making and     looping.</li> </ul>                                 |

# 9. SUGGESTED SPECIFICATION TABLE FOR QUESTION PAPER DESIGN

| Unit | Unit Title                                             | Teaching | Distri | bution o | f Theory | Marks |

|------|--------------------------------------------------------|----------|--------|----------|----------|-------|

| No.  |                                                        | Hours    | R      | U        | A        | Total |

|      |                                                        |          | Level  | Level    | Level    | Marks |

| I    | Number systems, Digital Logic families and Logic Gates | 12       | 2      | 4        | 10       | 16    |

| II   | Combinational Logic Circuits                           | 14       | 2      | 4        | 8        | 14    |

| III  | Sequential Logic Circuits                              | 12       | 2      | 4        | 6        | 12    |

| IV   | Microprocessor: 8086 and Modern Microprocessors        | 12       | 2      | 4        | 6        | 12    |

| V    | Assembly Language Programming using 8086.              | 14       | 0      | 4        | 12       | 16    |

|      | Total                                                  | 64       | 8      | 20       | 42       | 70    |

**Legends:** R=Remember, U=Understand, A=Apply and above (Bloom's Revised taxonomy) Note: This specification table provides general guidelines to assist student for their learning and to teachers to teach and assess students with respect to attainment of UOs. The actual distribution of marks at different taxonomy levels (of R, U and A) in the question paper may vary from above table.

# 10. SUGGESTED STUDENT ACTIVITIES

Other than the classroom and laboratory learning, following are the suggested student-related *co-curricular* activities which can be undertaken to accelerate the attainment of the various outcomes in this course: Students should conduct following activities in group and prepare reports of about 5 pages for each activity, also collect/record physical evidences for their (student's) portfolio which will be useful for their placement interviews:

- a. Undertake micro-project.

- b. Prepare journals based on practical performed in laboratory.

- c. Find and Utilize web based / simulator, android applications related to Digital electronics. And microprocessor 8086.

- i. Undertake a market survey of different digital electronics based application and Microprocessors.

- ii. Prepare a block diagram of application (eg. Gesture recognition or motion detection (RASPBERRY PI/ARM PROCESSOR) using RISC architecture and co relate RISC characteristics.

### 11. SUGGESTED SPECIAL INSTRUCTIONAL STRATEGIES (if any)

These are sample strategies, which the teacher can use to accelerate the attainment of the various outcomes in this course:

- a. Massive open online courses (MOOCs) may be used to teach various topics/sub topics.

- b. 'L' in item No. 4 does not mean only the traditional lecture method, but different types of teaching methods and media that are to be employed to develop the outcomes.

- c. About 15-20% of the topics/sub-topics which is relatively simpler or descriptive in nature is to be given to the students for self-directed learning and assess the development of the COs through classroom presentations (see implementation guideline for details).

- d. With respect to item No.10, teachers need to ensure to create opportunities and provisions for *co-curricular activities*.

- e. Guide student(s) in undertaking micro-projects.

- f. Demonstrate students thoroughly before they start doing the practice.

- g. It is recommended to perform digital techniques practical on bread board.

- h. Guide and motivate student(s) in performing testing and troubleshooting and implementing programs.

# 12. SUGGESTED MICRO-PROJECTS

Only one micro-project is planned to be undertaken by a student that needs to be assigned to him/her in the beginning of the semester. In the first four semesters, the micro-project are group-based. However, in the fifth and sixth semesters, it should be preferably be individually undertaken to build up the skill and confidence in every student to become problem solver so that s/he contributes to the projects of the industry. In special situations where groups have to be formed for micro-projects, the number of students in the group should not exceed three.

The micro-project could be industry application based, internet-based, workshop-based, laboratory-based or field-based. Each micro-project should encompass two or more COs which are in fact, an integration of PrOs, UOs and ADOs. Each student will have to maintain dated work diary consisting of individual contribution in the project work and give a seminar presentation of it before submission. The total duration of the micro-project should not be less than 16 (sixteen) student engagement hours during the course. The student ought to submit micro-project by the end of the semester to develop the industry oriented COs.

A suggestive list of micro-projects are given here. Similar micro-projects could be added by the concerned faculty:

# For Digital Techniques: Student shall design, Assemble, Test and troubleshoot following micro projects

- a. Burglar alarm

- b. Freezer warning buzzer

- c. A push-button lock

- d. A light-activated burglar alarm

- e. A safety thermostat

- f. An automatic watering system

For Microprocessor: Students shall simulate program using assembler.

- a. Checker's Board using 8X 8 Matrix.

- b. Chess Board using 8X 8 Matrix

# 13. SUGGESTED LEARNING RESOURCES

| S.<br>No. | Title of Book                                     | Author                                                  | Publication                                                        |

|-----------|---------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|

| 1         | Modern Digital<br>Electronics                     | Jain R.P.                                               | McGraw Hill Education, New Delhi, 2016 ISBN(13): 978-0-07-066911-6 |

| 2         | Digital Principles and<br>Applications            | Leach Donald P,<br>Malvino Albert Paul,<br>Saha Gautam. | McGraw Hill Education New Delhi, 2016, ISBN: 978-93-392-0341-2     |

| 3         | Advanced<br>Microprocessor And<br>Peripherals 3/E | Bhurchandi Kallor rec                                   | McGraw Hill Education New Delhi, 2016, ISBN: 9781259006135         |

| S.<br>No. | Title of Book                                       | Author        | Publication                                           |

|-----------|-----------------------------------------------------|---------------|-------------------------------------------------------|

| 4         | 8086 Programming and advance processor architecture | Savaliya M.T. | Wiley India, New Delhi, 2013, ISBN: 978-81-265-3091-5 |

# 14. SUGGESTED SOFTWARE/ LEARNING WEBSITES

- a. http://www.electrical4u.com/some-common-applications-of-logic-gates/

- b. http://www.zeepedia.com/toc.php?digital logic design&b=9

- c. http://www.cburch.com/logisim

- d. http://www.logiccircuit.org/download.html

- e. http://www.learnabout-electronics.org/Digital/dig42.php

- f. http://www.electrical4u.com/jk-flip-flop/

- g. http://ce.kashanu.ac.ir/sabaghian/assembly/8086%20tutorial/8086%20Assembler%20Tu torial%20for%20Beginners%20(Part%201).htm

- h. http://www.firmcodes.com/difference-risc-sics-architecture/

- i. http://www.arm.com/products/processors/instruction-set-architectures/index.php

- j. https://en.wikipedia.org/wiki/ARM\_architecture

- k. http://www.botskool.com/user-pages/tutorials/electronics/arm-7-tutorial-part-1

- 1. http://meseec.ce.rit.edu/551-projects/fall2012/1-1.pdf

- m. www.intel.com